What is embedded FPGA (eFPGA?)

eFPGA is a digital block you can embed in your SoC like an ARM or RISC-V processor.

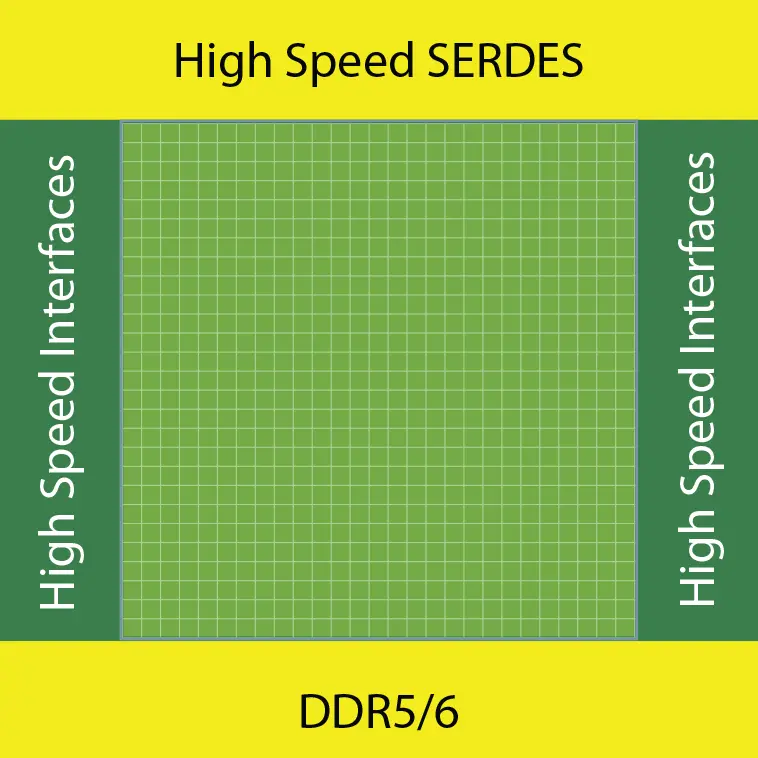

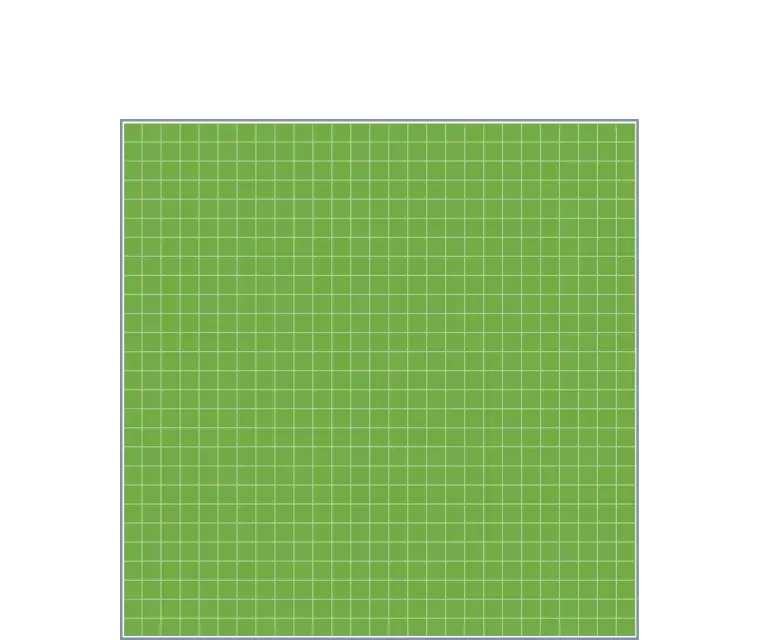

It’s like the digital core of a standard FPGA chip: you eliminate the expensive FPGA package, and you eliminate the power-hungry SERDES/PHYs leaving just the digital logic.

eFPGA can deliver the same speed and density as the FPGA you replace (in the same process node).

But unlike FPGA which comes with a limited number of sizes and a fixed ratio of logic/DSP/RAM, you can get the exact size you want with the exact amount of logic/DSP/RAM you want in any process node.

Flex Logix has been delivering eFPGA hardware and software tools for years to dozens of customers with >20 working chips and dozens more in design.